# VLSI Design Basics

#### Yu Bi

ELE594 – Special Topic on Hardware Security & Trust University of Rhode Island

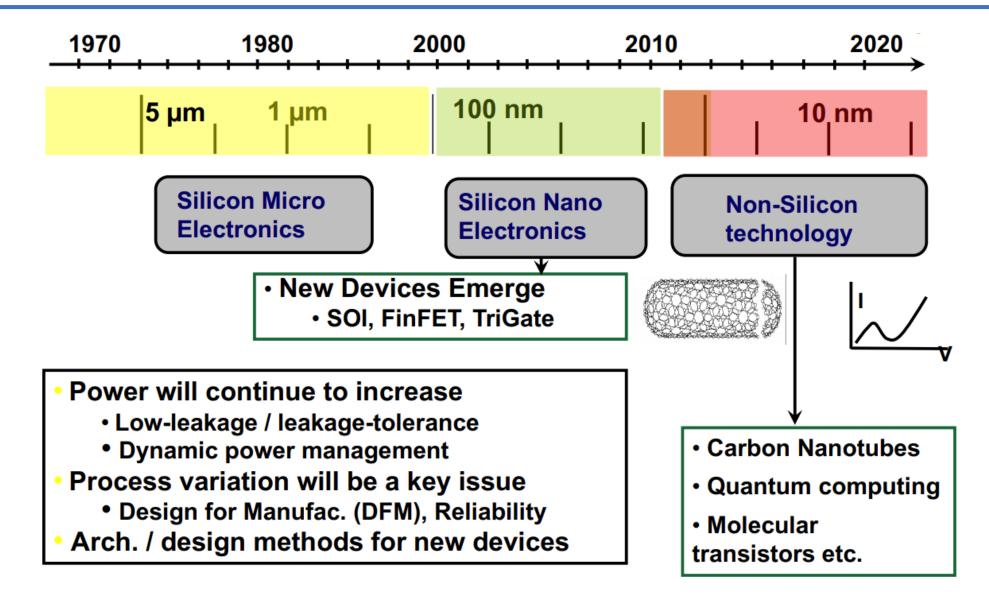

### Semiconductor Roadmap

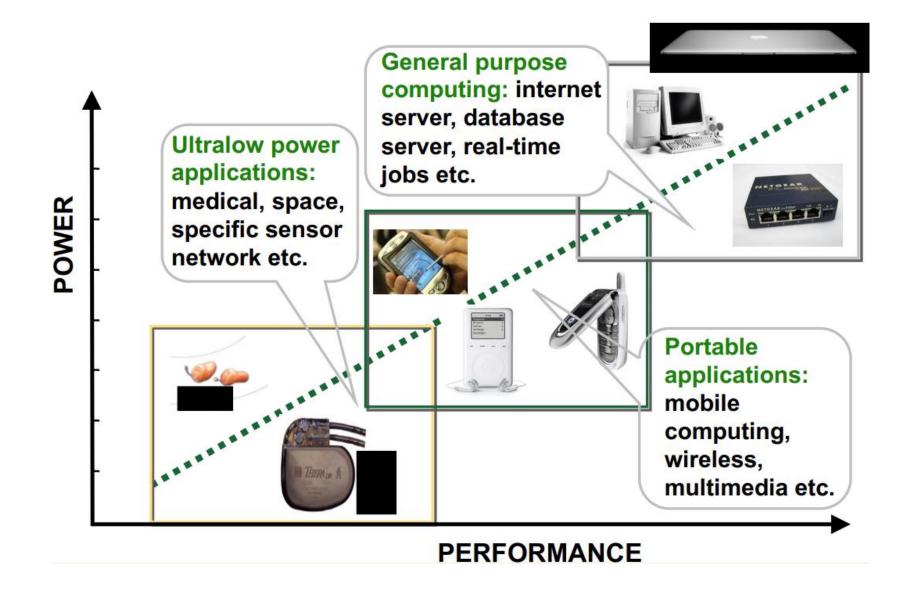

#### **VLSI** Applications

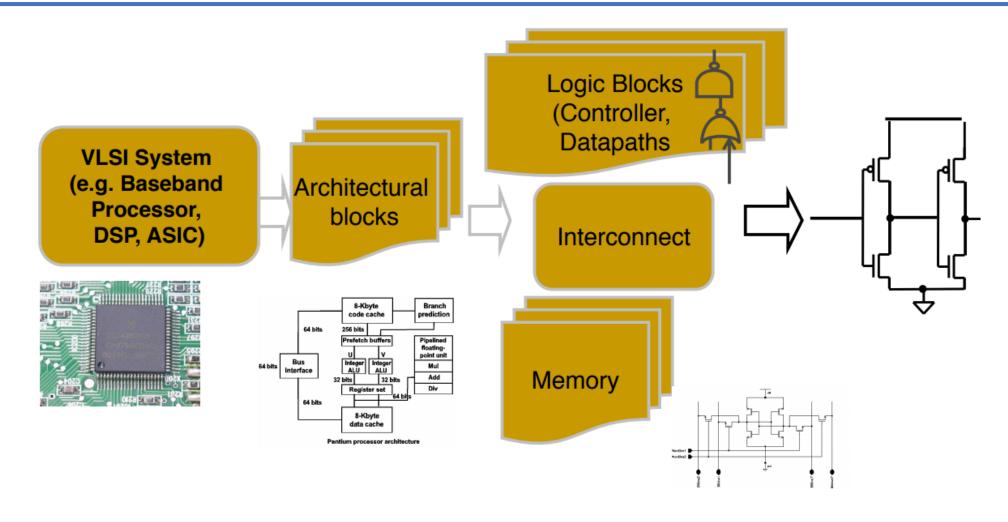

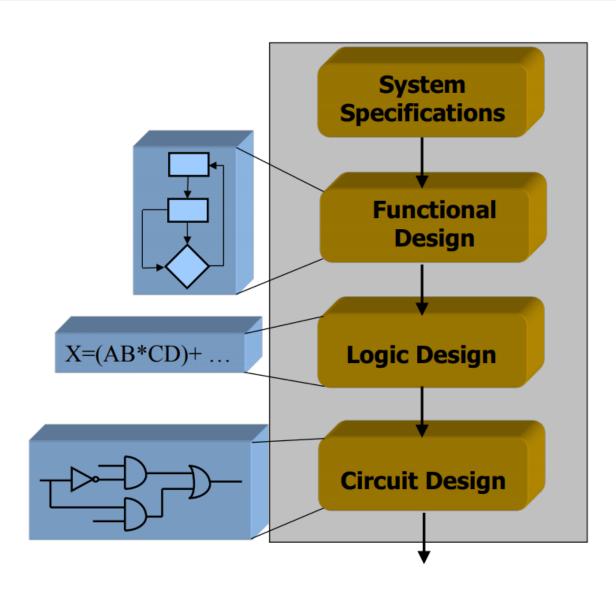

## VLSI System Breakdown

System -> Architecture -> Logic -> Transistor

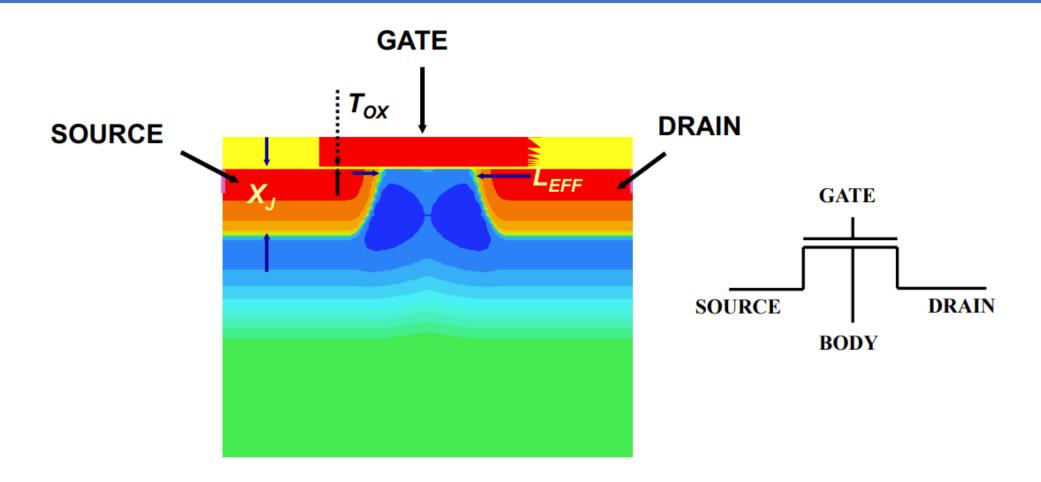

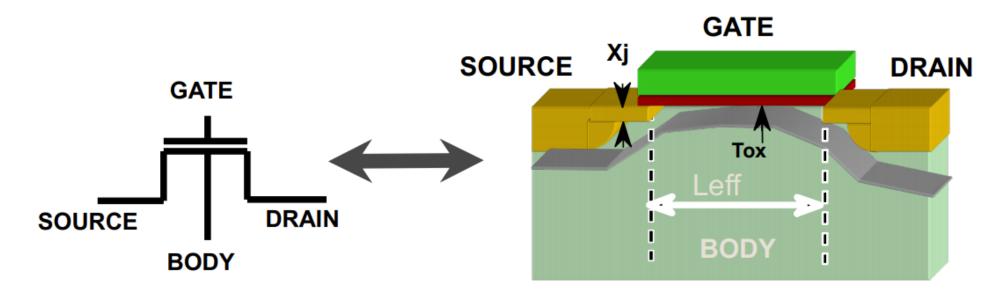

#### **Transistor**

- Underlying building unit for integrated circuit, e.g. logic gates and memory units

- Advanced commercial technology nowadays goes beyond 7 nm

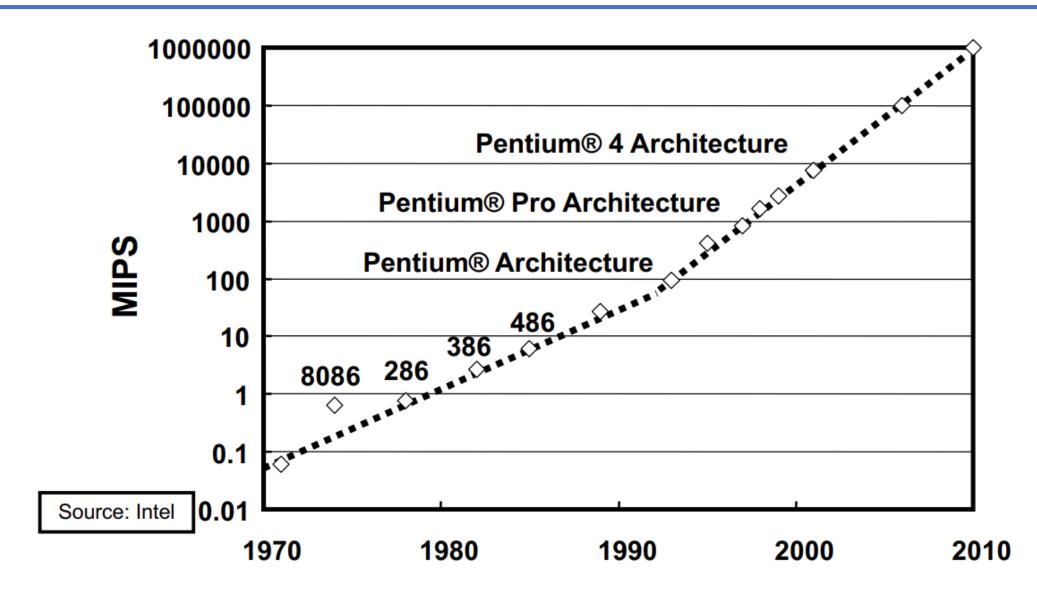

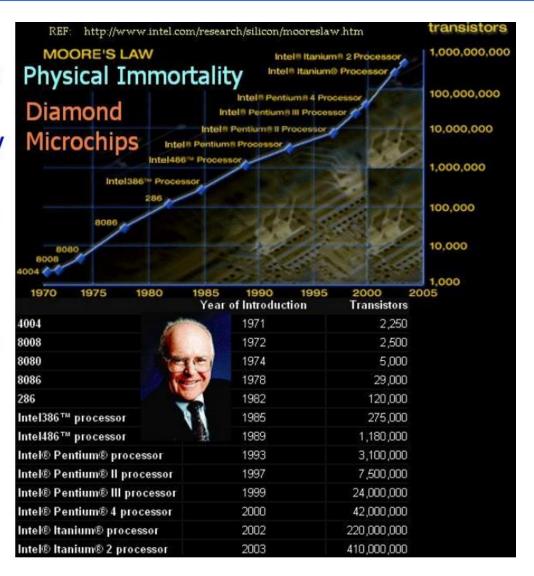

# Growth in Computing Power

#### Moore's Law

"The complexity for minimum component costs has increased at a rate of roughly a factor of two per year ... Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. ..."

Electronics Magazine, 19 April 1965

## Technology Scaling

| Dimensions scale down by 30% | Doubles transistor density            |

|------------------------------|---------------------------------------|

| Oxide thickness scales down  | Faster transistor, higher performance |

| Vdd & Vt scaling             | Lower active power                    |

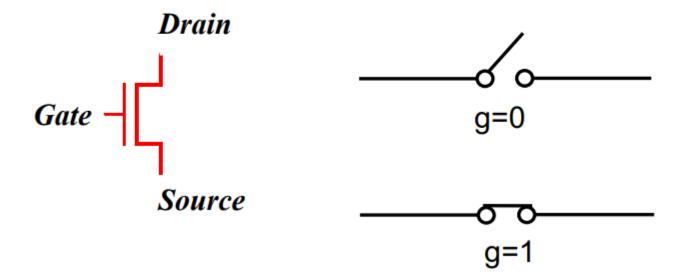

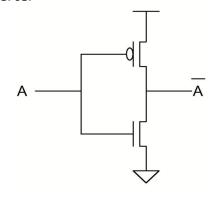

## N-type MOS Transistor

- If the gate is "high", the switch is on

- If the gate is "low", the switch is off

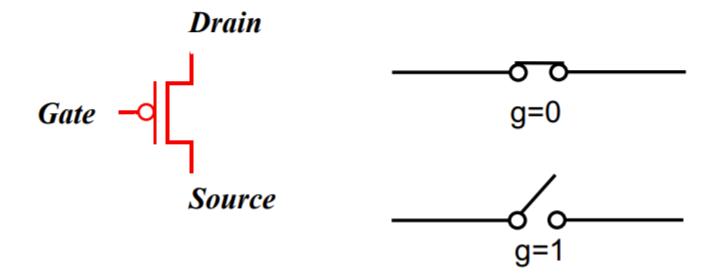

### P-type MOS Transistor

- If the gate is "low", the switch is on

- If the gate is "high", the switch is off

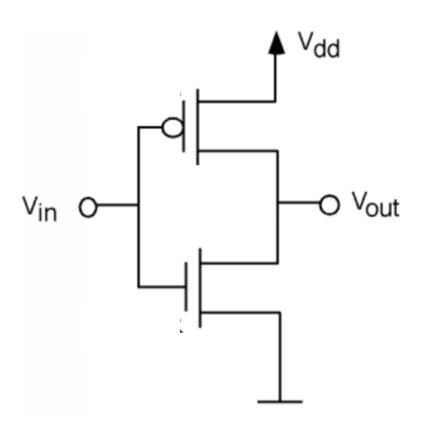

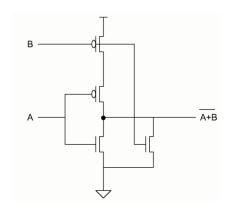

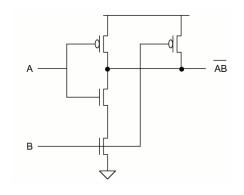

### **CMOS**

- No static current flow

- Less current means less power

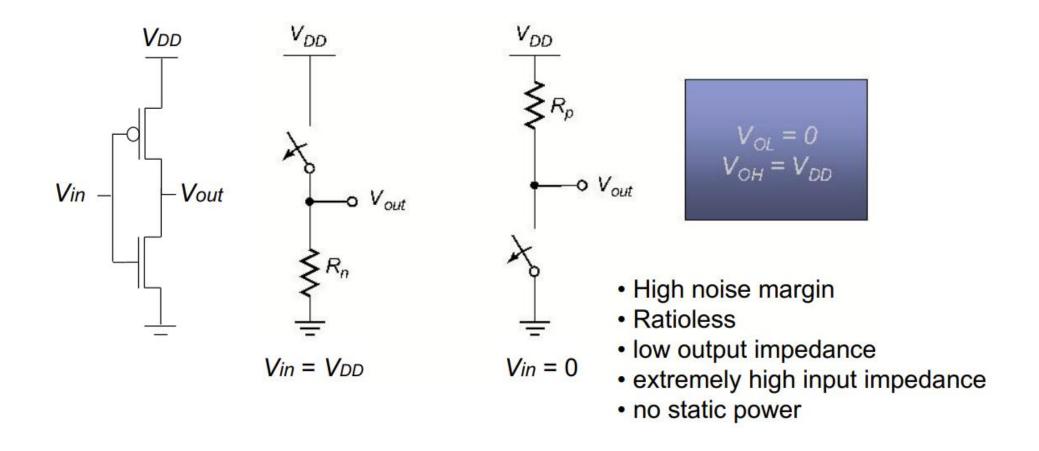

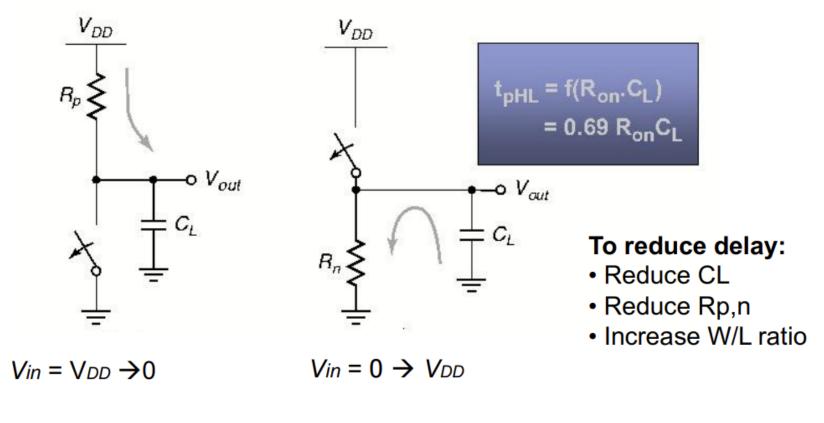

### **CMOS** Inverter Analysis

## **CMOS** Inverter Analysis

Output: Low-to-High High-to-Low

CL is composed of the drain diffusion capacitances of the NMOS and PMOS transistors, the capacitance of connecting wires, and the input capacitance of the fan-out gates

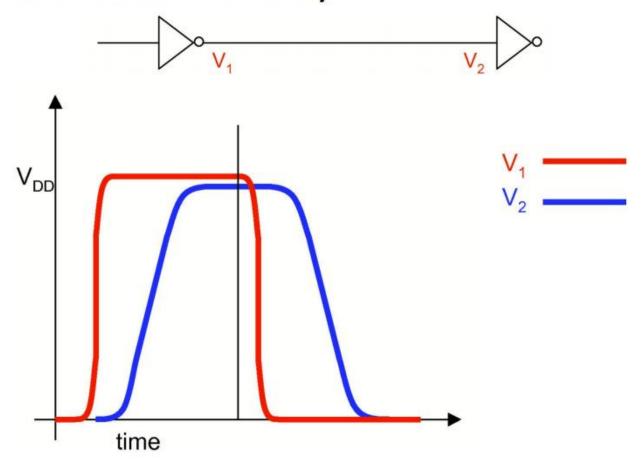

### **CMOS** Inverter Results

Interconnect delay

## Boolean Logic

- Basic operators

- AND

OR

$$f(A,B) = A + B = A \cup B$$

$$A \longrightarrow A+B$$

| Α | В   | A•B |  |

|---|-----|-----|--|

| 0 | 0 0 |     |  |

| 0 | 1   | 0   |  |

| 1 | 0   | 0   |  |

| 1 | 1   | 1   |  |

| Α | В | A+B |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 1   |

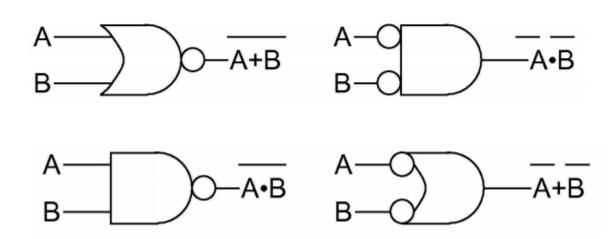

## Boolean Logic

#### Basic operators

#### NAND

$$f(A,B) = \overline{A \cdot B} = \overline{A \cap B}$$

$$A \longrightarrow \overline{A \cdot B}$$

$$B \longrightarrow \overline{A \cdot B}$$

| Α | В | A•B |  |

|---|---|-----|--|

| 0 | 0 | 1   |  |

| 0 | 1 | 1   |  |

| 1 | 0 | 1   |  |

| 1 | 1 | 0   |  |

#### NOR

$$f(A,B) = \overline{A+B} = \overline{A \cup B}$$

$$A \longrightarrow \overline{A+B}$$

| Α | В     | A+B |  |

|---|-------|-----|--|

| 0 | 0 0 1 |     |  |

| 0 | 1     | 0   |  |

| 1 | 0     | 0   |  |

| 1 | 1     | 0   |  |

## Boolean Logic

#### DeMorgan's Theorem

$$\overline{A+B} = \overline{A} \cdot \overline{B}$$

$$\overline{A \cdot B} = \overline{A} + \overline{B}$$

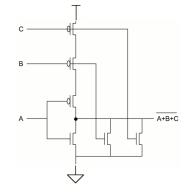

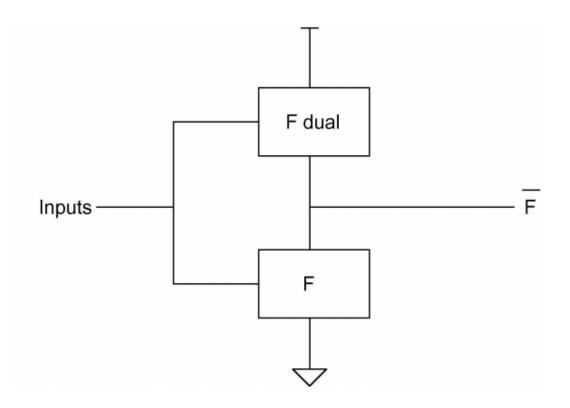

# CMOS Logic Implementation

Inverter

NOR

NAND

Multi-input NOR

## **CMOS** Logic Implementation

General CMOS combinational logic

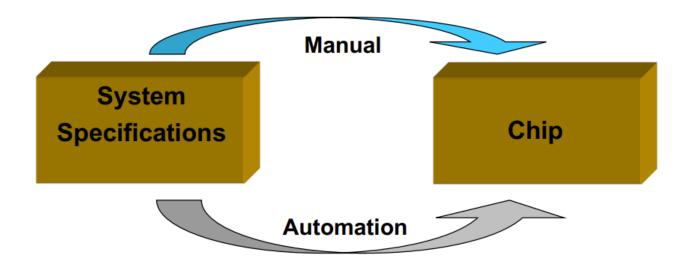

- Large number of components

- Optimize requirements for <u>higher performance</u>

- Performance relates to speed, power and size.

- Time to market competition

- Cost

- Using computer makes it cheaper by reducing time-to-market.

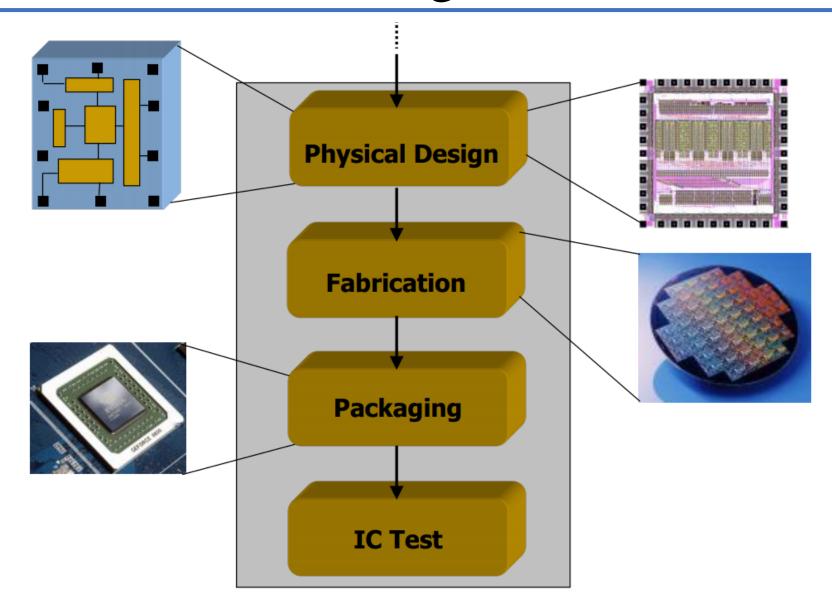

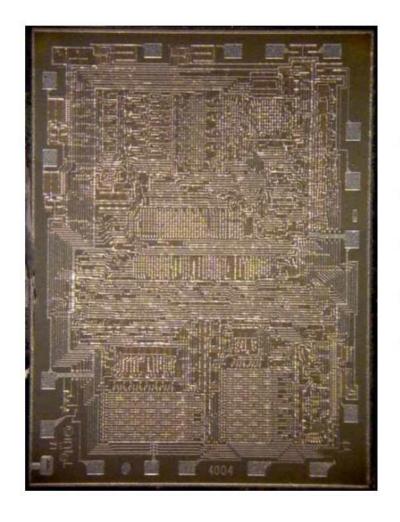

### Intel 4004

- First microprocessor

- Designed in 1971

- 2300 transistors

- 10-um process

- ~100 KHz

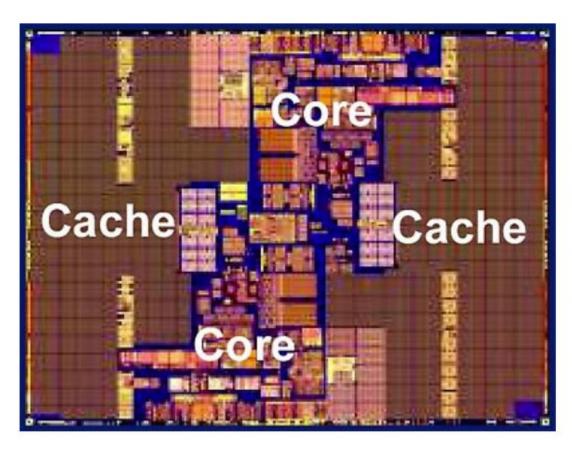

#### Intel Itanium Processor

- Released in 2005

- 1.72 Billion transistors

- 90-nm process

- 2 GHz

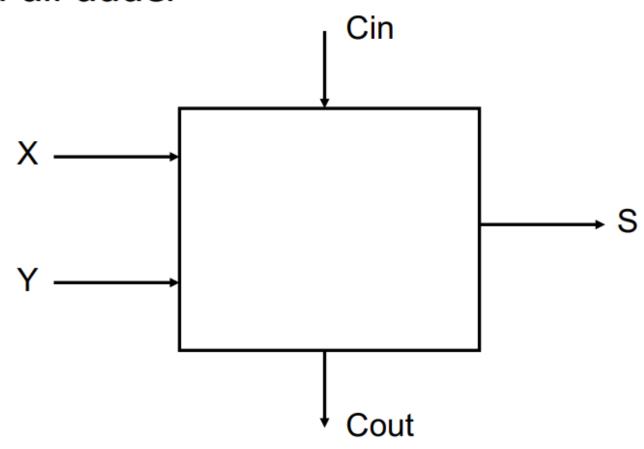

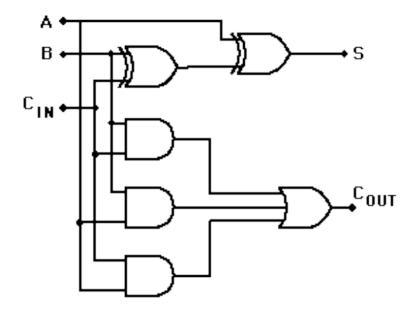

# Functional Specification

#### Full adder

## Behavioral Specification

- VHDL

- Verilog

```

entity adder is

-- i0, i1 and the carry-in ci are inputs of the adder.

-- s is the sum output, co is the carry-out.

port (i0, i1 : in bit; ci : in bit; s : out bit; co : out bit);

end adder;

architecture rtl of adder is

begin -- This full-adder architecture contains two concurrent assignment.

-- Compute the sum. s <= i0 xor i1 xor ci;

-- Compute the carry. co <= (i0 and i1) or (i0 and ci) or (i1 and ci);

end rtl;</pre>

```

## Behavioral Specification

```

module fulladder (a,b,cin,sum,cout);

input a,b,cin;

output sum, cout;

reg sum, cout;

always @ (a or b or cin)

begin

sum \le a ^b ^cin;

cout <= (a \& b) | (a \& cin) | (b \& cin);

end

endmodule

```

# Logic Design

#### Full Adder Truth Table

| CARRY<br>IN | input<br>B | input<br>A | CARRY<br>OUT | SUM<br>digit |

|-------------|------------|------------|--------------|--------------|

| 0           | 0          | 0          | 0            | 0            |

| 0           | 0          | 1          | 0            | 1            |

| 0           | 1          | 0          | 0            | 1            |

| 0           | 1          | ]          | 1            | 0            |

| 1           | 0          | 0          | 0            | 1            |

| 1           | 0          | 1          | 1            | 0            |

| 1           | 1          | 0          | 1            | 0            |

| 1           | 1          | 1          | 1            | 1            |

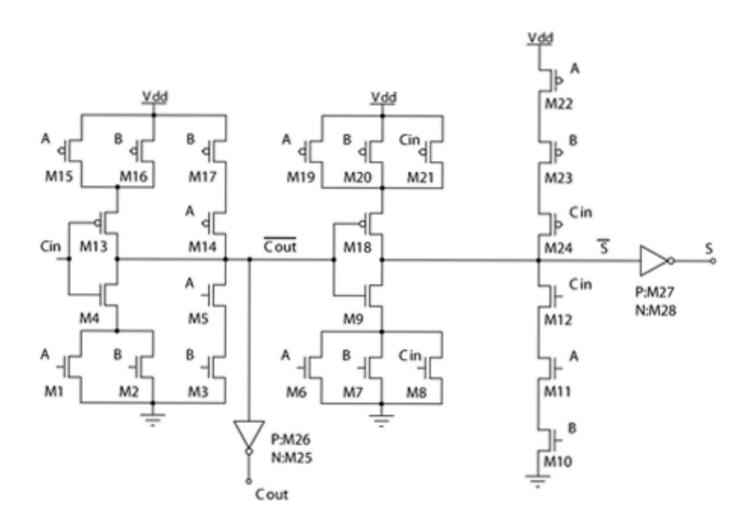

### **Transistor Schematic**

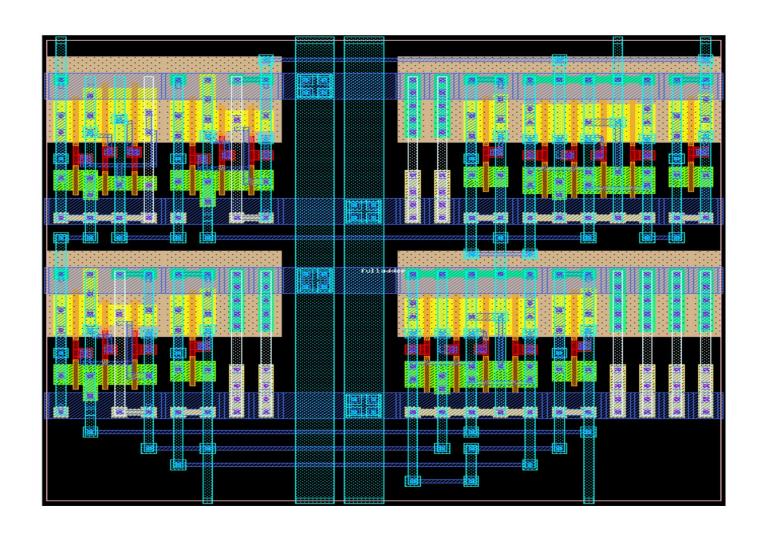

# Layout

## VLSI Design Approaches

- Full custom

- Design for performance-critical cells

- Very expensive

- Standard cell

- Faster

- Performance is not as good as full custom

- Gate array

- Field Programmable Gate Array

# VLSI Design Approaches

|                    | Full<br>Custom               | Standard<br>Cell               | Gate Array                     | FPGA                        |

|--------------------|------------------------------|--------------------------------|--------------------------------|-----------------------------|

| Area               | Compact                      | Moderate                       | Moderate                       | Large                       |

|                    |                              |                                |                                |                             |

| Performance        | High                         | Moderate                       | Moderate                       | Low                         |

|                    |                              |                                |                                |                             |

| Production Volume: | Mass<br>Production<br>Volume | Medium<br>Production<br>Volume | Medium<br>Production<br>Volume | Low<br>Production<br>Volume |

| <b>Complexity:</b> | High                         |                                |                                | Low                         |

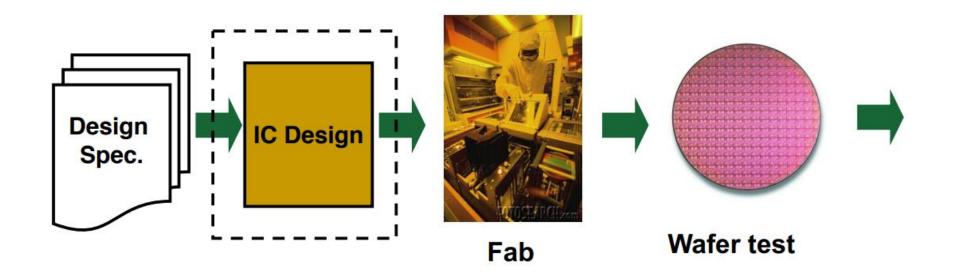

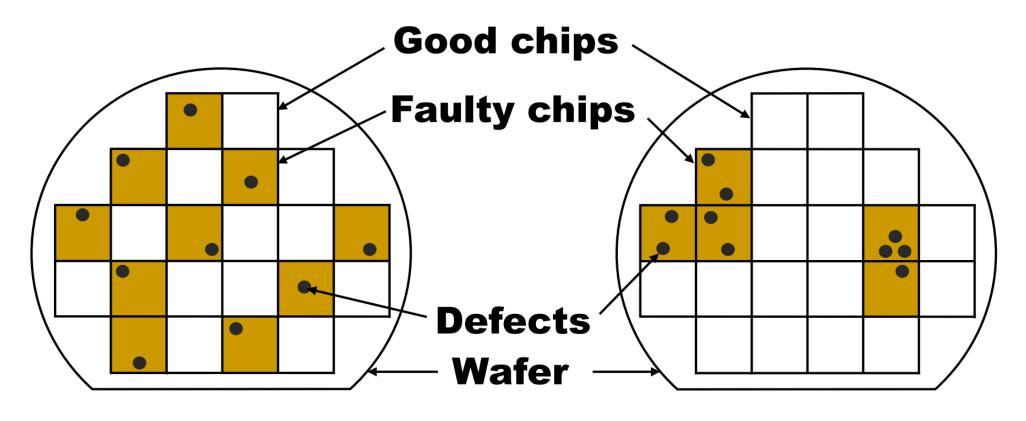

### Chip Yield

- A manufacturing defect in the fabrication process causes electrically malfunctioning circuitry.

- A chip with no manufacturing defect is called a good chip.

- The defective ones are called bad chips.

- Percentage of good chips produced in a manufacturing process is called the *yield*.

- Yield is denoted by symbol Y.

How to separate bad chips from the good ones?

## Chip Yield

Unclustered defects

Wafer yield = 12/22 = 0.55

Clustered defects (VLSI) Wafer yield = 17/22 = 0.77

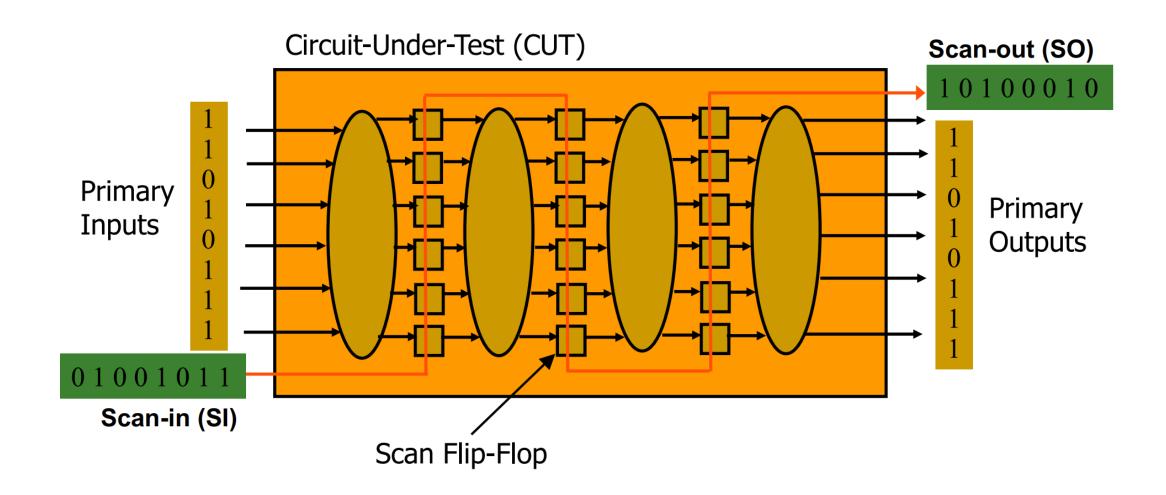

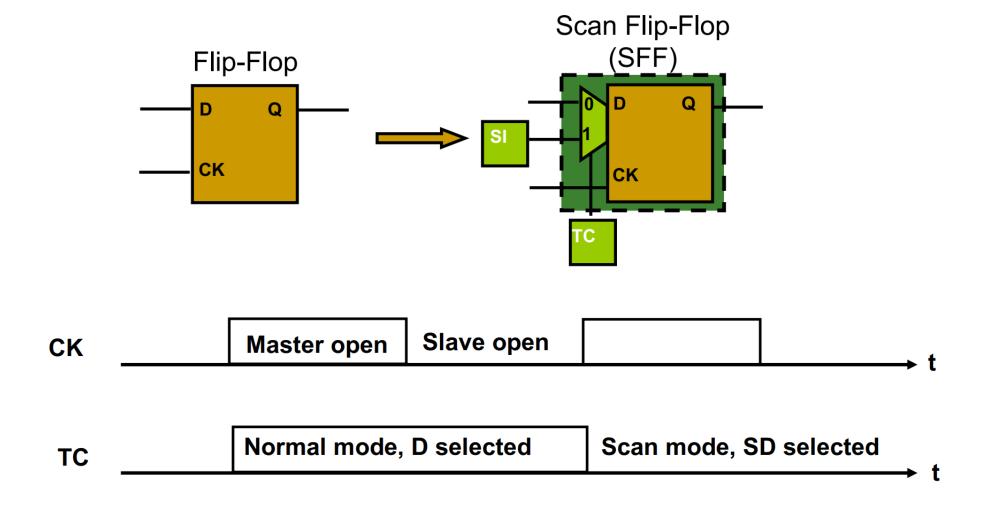

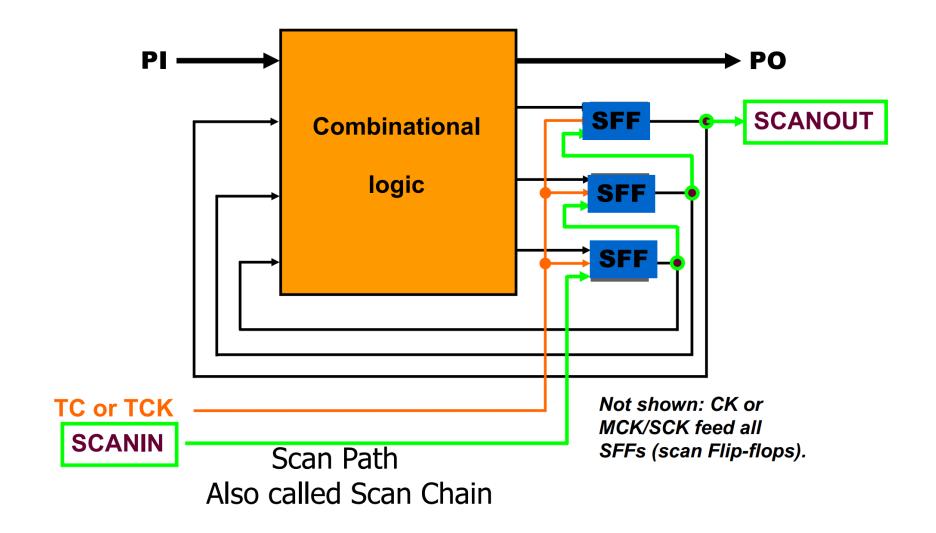

#### Scan Chain

#### Scan Chain

#### Scan Chain